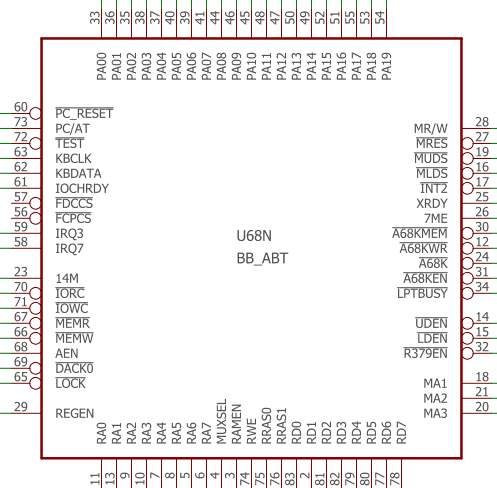

Address Bus Translator

Pin Description

| Pin | Type | Symbol | Function |

|---|---|---|---|

| 1 | I | VSS | GND |

| 2 | I/O | RD1 | D1 DPRAM |

| 3 | O | /RAMEN | Dual Port RAM Enable |

| 4 | I | /MUXSEL | Delayed feedback 50ns from /RAMEN Pin 3 |

| 5 | O | RA6 | Zorro Addressbus 7/15 multiplexed by MUXSEL |

| 6 | O | RA7 | Zorro Addressbus 8/16 multiplexed by MUXSEL |

| 7 | O | RA4 | Zorro Addressbus 5/13 multiplexed by MUXSEL |

| 8 | O | RA5 | Zorro Addressbus 6/14 multiplexed by MUXSEL |

| 9 | O | RA2 | Zorro Addressbus 3/11 multiplexed by MUXSEL |

| 10 | O | RA3 | Zorro Addressbus 4/12 multiplexed by MUXSEL |

| 11 | O | RA0 | Zorro Addressbus 1/9 multiplexed by MUXSEL |

| 12 | I | /A68KWR | Control Line from DBT |

| 13 | O | RA1 | Zorro Addressbus 2/10 multiplexed by MUXSEL |

| 14 | O | /UDEN | Control Line to DBT |

| 15 | O | /LDEN | Control Line to DBT |

| 16 | I | /MLDS | /LDS from Zorro Slot Lower Data Strobe selects data bits D0-D7 |

| 17 | O | /INT2 | Connected to Zorro Slot Pin 19 |

| 18 | I | MA1 | Zorro Addressbus 1 |

| 19 | I | /MUDS | /UDS from Zorro Slot Upper Data Strobe selects data bits D8-D15 |

| 20 | I | MA3 | Zorro Addressbus 3 |

| 21 | I | MA2 | Zorro Addressbus 2 |

| 22 | I | VSS | |

| 23 | I | 14M | 14.31818 MHz from ISA Bus B30 |

| 24 | I | /A68K | Connected from DBT Pin 75 |

| 25 | O | XRDY | Connected to Zorro Slot Pin 18 |

| 26 | I | 7ME | Connected to Zorro Slot Pin 92 |

| 27 | I | /MRES | Connected to Zorro Slot Pin 94 (/BUSRST) |

| 28 | I | /MR/W | Connected to Zorro Slot Pin 68 (R/W) |

| 29 | I | /REGEN | From DBT Pin 40 inverted an gated by MA3 and RCAS |

| 30 | I | /A68KMEM | Connected from DBT Pin 36 |

| 31 | O | /A68KEN | Enable 68k Adresslines [MA1..16] to RA[0..7] via MUX to DPRAM Adresslines |

| 32 | O | /R379N | Maybe Status Register Printer Port 1? |

| 33 | I | PA0 | Connected to ISA Slot A31 (A0) |

| 34 | O | /LPTBUSY | Connected to DBT Pin35 (inverted) |

| 35 | I | PA2 | Connected to ISA Slot A29 (A2) |

| 36 | I | PA1 | Connected to ISA Slot A30 (A1) |

| 37 | I | PA4 | Connected to ISA Slot A27 (A4) |

| 38 | I | PA3 | Connected to ISA Slot A28 (A3) |

| 39 | I | PA6 | Connected to ISA Slot A25 (A6) |

| 40 | I | PA5 | Connected to ISA Slot A26 (A5) |

| 41 | I | PA7 | Connected to ISA Slot A24 (A7) |

| 42 | I | VDD | |

| 43 | I | VSS | |

| 44 | I | PA8 | Connected to ISA Slot A23 (A8) |

| 45 | I | PA10 | Connected to ISA Slot A21 (A10) |

| 46 | I | PA9 | Connected to ISA Slot A22 (A9) |

| 47 | I | PA12 | Connected to ISA Slot A19 (A12) |

| 48 | I | PA11 | Connected to ISA Slot A20 (A11) |

| 49 | I | PA14 | Connected to ISA Slot A17 (A14) |

| 50 | I | PA13 | Connected to ISA Slot A18 (A13) |

| 51 | I | PA16 | Connected to ISA Slot A15 (A16) |

| 52 | I | PA15 | Connected to ISA Slot A16 (A15) |

| 53 | I | PA18 | Connected to ISA Slot A13 (A18) |

| 54 | I | PA19 | Connected to ISA Slot A12 (A19) |

| 55 | I | PA17 | Connected to ISA Slot A14 (A17) |

| 56 | O | /FCPCS | Floppy Controller Port CS used only on A2088XT |

| 57 | O | /FDCCS | Floppy Disc Controller CS used only on A2088XT |

| 58 | O? | /IRQ7 | Connected to ISA Slot B21 |

| 59 | O? | /IRQ3 | Connected to ISA Slot B25 |

| 60 | O | /PC_RESET | Connected to RES_IN Chipset |

| 61 | O | IOCHRDY | Synced with CLK, buffered and Connected to ISA Slot B10 |

| 62 | I/O | KBDATA | |

| 63 | I/O | KBCLK | |

| 64 | I | VSS | |

| 65 | I | /LOCK | From CPU indicates that other system bus masters are not to gain control of the system bus while LOCK is active (LOW). The LOCK signal is activated by the ‘‘LOCK’’ prefix instruction and remains active until the completion of the next instruction. This signal is active LOW, and floats to 3-state off in ‘‘hold acknowledge’’. |

| 66 | I | /MEMW | Mem Write Lower Megabyte (/SMEMW) from ISA SLOT Pin B11 A2286 & A2386 sync this Signal by SYSCLK |

| 67 | I | /MEMR | Mem Read lower Megabyte (/SMEMR) from ISA SLOT Pin B12 A2286 & A2386 sync this Signal by SYSCLK |

| 68 | I | AEN | Connected to ISA Slot A11 |

| 69 | I | /DACK0 | Connected to ISA Slot B19 |

| 70 | I | /IORC | Connected to ISA Slot B14 |

| 71 | I | /IOWC | Connected to ISA Slot B13 |

| 72 | I | /TEST | 1= Normal Mode 0=??? |

| 73 | I | PC/AT | 0=AT 1=PC |

| 74 | O | /RWE | Write Enable DP-RAM |

| 75 | O | /RRAS0 | RAS DPRAM High Byte |

| 76 | O | /RRAS1 | RAS DPRAM Low Byte |

| 77 | I/O | RD6 | D6 DPRAM |

| 78 | I/O | RD7 | D7 DPRAM |

| 79 | I/O | RD4 | D4 DPRAM |

| 80 | I/O | RD5 | D5 DPRAM |

| 81 | I/O | RD2 | D2 DPRAM |

| 82 | I/O | RD3 | D3 DPRAM |

| 83 | I/O | RD0 | D1 DPRAM |

| 84 | I | VDD |

Last Change: 31.07.2023